การรัน quantum circuit

ดูวิดีโอเกี่ยวกับ quantum circuit และ primitive จาก Olivia Lanes หรือเปิดวิดีโอในหน้าต่างแยกบน YouTube.

ภาพรวมบทเรียน

บทเรียนนี้จะเป็นภาพรวมระดับสูงของพื้นฐานการรันการประมวลผลควอนตัมระดับ utility scale ตั้งแต่ฮาร์ดแวร์ควอนตัมที่ใช้ไปจนถึงหลักการที่ควรพิจารณาเมื่อออกแบบ quantum circuit ตามหลักการแล้ว เมื่อจบบทเรียนนี้ คุณจะรู้:

-

คอมพิวเตอร์ควอนตัม IBM® จริง ๆ แล้วคืออะไร คุณจะต้องรู้พื้นฐานของคุณสมบัติฮาร์ดแวร์เพื่อออกแบบ quantum circuit ของคุณอย่างเหมาะสมที่สุดสำหรับการรัน

-

Qiskit คืออะไร primitive คืออะไร และเราสามารถใช้พวกมันสร้างและรัน quantum circuit ได้อย่างไร

-

ขั้นตอนการทำงานทั่วไปที่เราทำตามเพื่อรันการทดลองในระดับ scale ซึ่งรวมถึงการเลือก primitive ที่ดีที่สุดสำหรับ use case ของคุณ การ map ปัญหาสู่ quantum circuit และการใช้การลดข้อผิดพลาดและการระงับข้อผิดพลาด ซึ่งช่วยให้เราสามารถดึงพลังงานออกจากเครื่องจักรเหล่านี้ได้มากที่สุด

ฮาร์ดแวร์ – โปรเซสเซอร์ควอนตัม IBM

เพื่อเข้าใจวิธีที่เราสามารถทำการเลือกที่เหมาะสมในการออกแบบ quantum circuit ขนาดใหญ่ เราต้องรู้เล็กน้อยเกี่ยวกับฮาร์ดแวร์จริงที่จะรัน circuit เหล่านี้ มาพูดถึง physical Qubit และโปรเซสเซอร์ควอนตัม IBM กันสั้น ๆ

โปรเซสเซอร์ควอนตัม IBM สร้างโดยใช้ superconducting transmon Qubit ซึ่งเป็นวงจรไฟฟ้าที่ประกอบด้วย Josephson junction และ capacitor ต่อขนานกัน Josephson junction เป็น nonlinear inductor ที่สร้างจากสองชั้นของโลหะ superconducting ที่ทับซ้อนกันพร้อม insulating barrier ระหว่างพวกมัน ที่อุณหภูมิต่ำมาก อิเล็กตรอนใน superconductor จับคู่กันเพื่อสร้างสิ่งที่เรียกว่า cooper pair Cooper pair สามารถ tunnel ผ่าน insulating barrier จากด้านหนึ่งของ junction ไปอีกด้านหนึ่งได้โดยธรรมชาติ พฤติกรรม tunneling นี้ก่อให้เกิดคุณสมบัติ nonlinear ที่สร้าง Qubit ของเรา

Microwave transmission line ถูกสร้างบนชิปเพื่อส่ง microwave signal ไปยัง Qubit เมื่อเราใช้ microwave pulse ที่ถูกปรับเทียบอย่างแม่นยำซึ่งมีความถี่ แอมพลิจูด รูปร่าง และระยะเวลาเฉพาะกับสาย เราสามารถทำให้ Qubit ทำสิ่งเฉพาะได้ สิ่งนี้เป็นพื้นฐานของ quantum Gate ของเรา เราสร้างชิปให้ Qubit ที่อยู่ใกล้กันเชื่อมต่อในโครงสร้างแลตทิซเฉพาะที่เรียกว่า heavy-hex lattice การเชื่อมต่อนี้ ที่เรียกว่า topology ของโปรเซสเซอร์เรา เป็นปัจจัยสำคัญที่ต้องพิจารณาเมื่อออกแบบ circuit ดังที่เราจะพูดถึงในบทเรียนต่อมา

คำสั่งสำหรับ microwave pulse ไปจากคอมพิวเตอร์ของคุณ ผ่านคลาวด์ และไปยังอิเล็กทรอนิกส์ควบคุมที่อุณหภูมิห้อง ซึ่งตีความคำสั่งเหล่านั้นและสร้าง pulse ทางกายภาพ หลังจากกล่องควบคุมที่อุณหภูมิห้องสร้าง pulse แล้ว พวกมันเดินทางผ่านสายเคเบิลเข้าสู่ dilution refrigerator และใ�นที่สุดก็ไปถึงชิปควอนตัม สัญญาณเข้าสู่ resonator ผ่าน wirebond และจากนั้นไหลลงตาม transmission line เข้าสู่ Qubit ของเรา

IBM มีคอมพิวเตอร์ควอนตัมหลายสิบเครื่องทั่วโลก และเราได้อัปเกรดกองยาน recently เพื่อมีเฉพาะโปรเซสเซอร์ที่ใหญ่กว่า 100 Qubit บางส่วนตั้งอยู่ในศูนย์ข้อมูลควอนตัม IBM ใน upstate New York และปรับใช้ผ่านคลาวด์สำหรับทุกคนใช้งาน และบางส่วนเป็นระบบ on-premises เฉพาะที่รองรับพาร์ทเนอร์ในเครือข่าย IBM Quantum® คุณสามารถล็อกอินที่ quantum.cloud.ibm.com เพื่อดูว่าโปรเซสเซอร์ใดที่คุณมีสิทธิ์เข้าถึง

แต่ละโปรเซสเซอร์แสดง metrics ประสิทธิภาพสามอย่าง ซึ่งเราพูดถึงในบทเรียนก่อนหน้า แต่เป็นการเตือนความจำ: qubit count, EPLG, และ CLOPS

-

Qubit count นี่อธิบายตัวเอง: มันคือจำนวน Qubit ทั้งหมดที่มีให้ใช้บนโปรเซสเซอร์ควอนตัมเดียว สำหรับปัญหาขนาดใหญ่ที่ utility-scale คุณจะต้องแน่ใจว่าคุณใช้โปรเซสเซอร์ที่มี Qubit เพียงพอในการจัดการกับปัญหา แต่ qubit count เพียงอย่างเดียวไม่ใช่สิ่งเดียวที่สำคัญ

-

EPLG หรือ "errors per layered gate" นี่เป็นการวัดคุณภาพของ Qubit และ quantum Gate วัดข้อผิดพลาดเฉลี่ยที่แต่ละ Gate แนะนำใน circuit ที่สร้าง entanglement ระหว่าง Qubit ที่อยู่ติดกันในสายของ 100 Qubit คุณต้องการให้สิ่งนี้น้อยที่สุดเท่าที่จะเป็นไปได้

-

CLOPS หรือ "circuit layer operations per second" นี่วัดความเร็วของโปรเซสเซอร์ วัดจำนวน layer ของ benchmarking circuit บางอย่างที่เรียกว่า quantum volume circuit ที่ quantum processing unit (QPU) สามารถรันได้ต่อหน่วยเวลา ยิ่งตัวเลขสูง เราสามารถคำนวณได้เร็วขึ้น

ความสำคัญของแต่ละ metric เหล่านี้แตกต่างกันไปขึ้นอยู่กับการประยุกต์ใช้เฉพาะ และในบทเรียนอนาคต เราจะดูตัวอย่างจริงเพื่อดูว่าแต่ละปัจจัยเหล่านี้สามารถส่งผลต่อผลลัพธ์ของการคำนวณได้อย่างไร

ซอฟต์แวร์: Qiskit และ Qiskit Runtime

เพื่อเปลี่ยนปัญหาควอนตัมของคุณเป็นคำสั่งสำหรับคอมพิวเตอร์ควอนตัม คุณจะใช้ Qiskit ซึ่งเป็น open-source software development kit ที่ออกแบบมาสำหรับการทำงานบนคอมพิวเตอร์ควอนตัมที่พัฒนาโดย IBM ยังมี Qiskit Ecosystem ซึ่งเป็นคอลเลกชั่นของ software tutorial และฟังก์ชันที่สร้างหรือขยายบนฟังก์ชันหลักของ Qiskit และ Qiskit Runtime ซึ่งเป็นบริการการประมวลผลควอนตัมและ programming model ที่ช่วยให้ผู้ใช้สามารถออกแบบและปรับให้เหมาะสม quantum workload ของตนและรันพวกมันอย่างมีประสิทธิภาพโดยใช้ Qiskit Runtime Primitives

Primitive คือ building block ขนาดเล็กที่คุณสามารถใช้ออกแบบ circuit หรือ job ขนาดใหญ่ Primitive สองตัวที่สำคัญที่สุดสำหรับเราคือ Sampler และ Estimator ซึ่งเราจะพูดถึงในเชิงลึกในไม่ช้า

ด้วย Qiskit v1.0 ที่เพิ่งเปิดตัว Qiskit มีประสิทธิภาพและมีเสถียรภาพมากกว่าเดิม ดังนั้นสำหรับผู้ที่เพิ่งเริ่มต้น คุณมาถูกเวลาแล้ว! สำหรับผู้ที่คุ้นเคยกับ Qiskit อยู่แล้ว คุณจะต้องดาวน์โหลดและติดตั้งเวอร์ชันใหม่ใหม่อีกครั้ง สำหรับคู่มือการติดตั้งฉบับสมบูรณ์ ดูที่คู่มือ Install Qiskit

Quantum Circuit

ตอนนี้เราพร้อมที่จะพูดถึงรากฐานของโปรแกรมควอนตัม: quantum circuit ส่วนนี้จะทำหน้าที่เพียงแค่เป็นการทบทวน ถ้าคุณไม่คุ้นเคยกับ quantum circuit เราแนะนำให้เรียนรู้เกี่ยวกับพวกมันในเชิงลึกมากขึ้นโดยดูที่บทเรียน Quantum Circuits ในคอร์ส "Basics of quantum information" ก่อนดำเนินต่อ

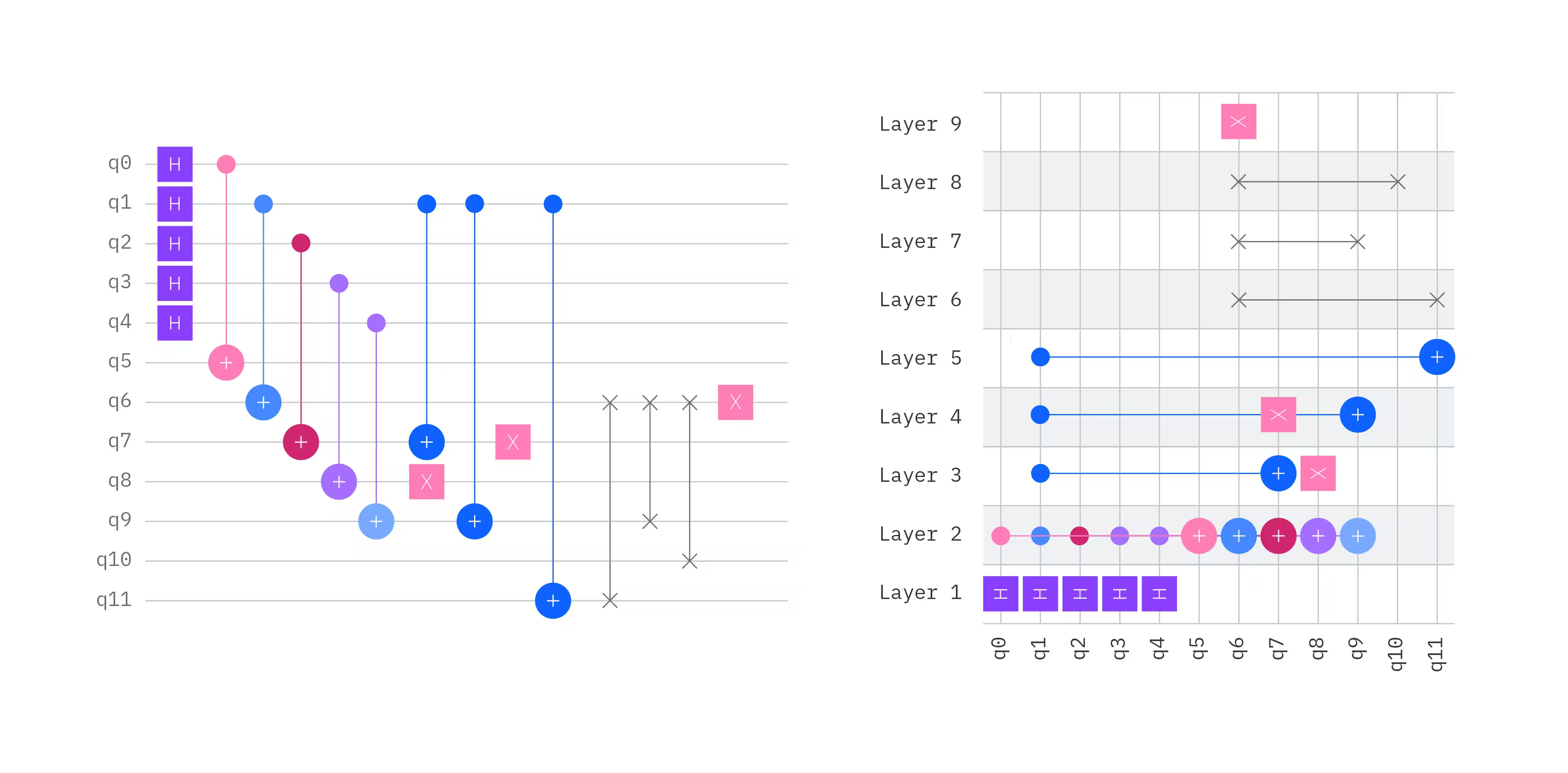

Quantum circuit คือเครือข่ายของ quantum Gate และการวัดที่เชื่อมโยงด้วยสายที่แสดงถึง Qubit ดั�งที่แสดงด้านล่าง Quantum circuit สามารถอ่านเหมือน sheet music จากซ้ายไปขวา เริ่มที่เวลา 0 ทางซ้าย Virtual Qubit ซึ่งยังไม่ได้รับการกำหนดให้เป็น physical Qubit บนโปรเซสเซอร์ จะแสดงในลำดับที่เพิ่มขึ้นจากบนลงล่าง

Gate แสดงด้วยสัญลักษณ์ต่าง ๆ บนสายของ Qubit ที่เกี่ยวข้อง Single-qubit Gate เช่น Hadamard Gate ที่แสดงด้านล่าง (กล่องที่มี H) ส่งผลต่อ Qubit ที่สายถูกวางไว้เท่านั้น Multi-qubit Gate เช่น CNOT Gate ที่แสดงด้วยเช่นกัน (เครื่องหมายบวกในวงกลมพร้อมเส้นเชื่อมต่อกับ q0) ส่งผลต่อ Qubit สองตัวขึ้นไป ใน CNOT Gate ที่แสดง สถานะของ q1 เปลี่ยนตามสถานะของ q0 หลังจาก Gate ทั้งหมดถูกดำเนินการแล้ว เราสามารถวัด Qubit ได้ ซึ่งบ่งชี้ด้วย Gate สีดำที่มีสัญลักษณ์การวัด ผลลัพธ์ของการวัดถูกเขียนลงบน classical register ซึ่งเป็นบัส "meas" แบบ double-line ด้านล่าง

ลักษณะสำคัญอย่างหนึ่งของ circuit คือความลึก ความลึกของ quantum circuit คือจำนวน "layer" ขั้นต่ำของ quantum Gate ที่รันแบบขนานที่จำเป็นในการทำ circuit ให้เสร็จสมบูรณ์ Quantum Gate สามารถรันแบบขนาน (ในเวลาเดียวกัน) ทุกครั้งที่พวกมันไม่มี Qubit ร่วมกัน แต่ถ้า Gate สองตัวขึ้นไปทำงานบน Qubit เดียวกัน เราไม่สามารถรันพวกมันแบบขนานได้ ต้องรันใน layer แยก ทีละอย่าง

มีอีกวิธีที่ไม่ชัดเจนนักในการกำหนดความลึกของ circuit โดยการเล่นเกมชนิดหนึ่ง กฎเป็นเรื่องง่าย: เริ่มจาก qubit wire ใดก็ได้ทางซ้าย คุณต้องเดินทางไปทางขวาและนับจำนวน Gate ที่คุณพบในเส้นทางของคุณ คุณสามารถกระโดดไปยัง wire ที่อยู่ติดกันได้เฉพาะเมื่อมันเชื่อมต่อกับ wire ปัจจุบันของคุณด้วย multi-qubit Gate เป้าหมายคือการสูงสุดจำนวน Gate ที่คุณพบตามเส้นทางของคุณ ตัวเลขสูงสุดนี้ยังเป็นความลึกของ circuit อีกด้วย

เนื่องจาก quantum Gate ต้องใช้เวลาในการใช้งาน ความลึกของ circuit สอดคล้องโดยประมาณกับเวลาที่คอมพิวเตอร์ควอนตัมต้องการในการรัน circuit เครื่องบางเครื่องเหมาะสมกว่าสำหรับ circuit ที่มีความลึกมากเนื่องจาก decoherence time ของ Qubit บนโปรเซสเซอร์ ดังนั้นเราต้องรู้ความลึกของ circuit เพื่อรู้ว่าสามารถรันบนอุปกรณ์เฉพาะได้หรือไม่

การออกแบบ quantum circuit: Qiskit patterns

แล้วเราจะออกแบบและรัน quantum circuit ได้อย่างไร? วิธีที่ง่ายที่สุดในการเข้าใจขั้นตอนการทำงานทั่วไปของการประมวลผลควอนตัมคือผ่าน Qiskit patterns Qiskit patterns เป็นกรอบแนวคิดที่ช่วยให้ผู้ใช้รัน quantum workload โดยการใช้ขั้นตอนบางอย่างด้วย modular tooling วิธีนี้ช่วยให้สามารถทำงานการประมวลผลควอนตัมได้โดย infrastructure การประมวลผล heterogeneous (CPU/GPU/QPU) ที่มีพลังงาน ขั้นตอนต่าง ๆ สามารถทำได้ as-a-service และสามารถรวม resource management ซึ่งช่วยให้สามารถผสมผสานความสามารถใหม่ ๆ ได้อย่างราบรื่นเมื่อพัฒนาขึ้น

ต่อไปนี้คือขั้นตอนหลัก ซึ่งผู้ใช้ Qiskit ที่มีประสบการณ์น่าจะจำได้

-

Map ขั้นตอนนี้กำหนดวิธีที่เราใช้ปัญหาทั่วไปที่สนใจและหาวิธี map มันสู่คอมพิวเตอร์ควอนตัมในรูปแบบของ quantum circuit

-

Optimize ในขั้นตอนนี้ เราใช้ Transpiler ของ Qiskit เพื่อ route และวางวาง circuit บนฮาร์ดแวร์ physical Qubit จริง ซึ่งรวมถึงการแปล quantum Gate แต่ละตัวเป็นลำดับของการดำเนินการที่ทำบนฮาร์ดแวร์ รวมถึงการปรับให้เหมาะสมในการวาง Gate

-

Execute Qiskit Runtime primitives ให้ interface กับฮาร์ดแวร์ IBM Quantum ที่ช่วยให้ transpiled circuit รันได้ ขั้นตอนนี้ยังรวมถึงการใช้เทคนิคการระงับและลดข้อผิดพลาด ซึ่งสามารถ abstract ออกจากผู้ใช้ได้เป็นส่วนใหญ่

-

Post-process ในขั้นตอนนี้ข้อมูลจากโปรเซสเซอร์ควอนตัมเองถูกประมวลผล ให้ผลลัพธ์ที่มีประโยชน์แก่ผู้ใช้สำหรับปัญหาเดิม โดยพื้นฐานแล้ว สิ่งนี้ครอบคลุมการวิเคราะห์เพิ่มเติมใด ๆ ของข้อมูลที่ได้รับ

Map

ขั้นตอน Map โดยพื้นฐานตั้งคำถามว่า "ฉันแปลปัญหาของฉันเป็น quantum circuit ที่สมเหตุสมผลที่จะรันบนฮาร์ดแวร์ควอนตัมได้อย่างไร?" ไม่ต้องสงสัยเลย: การ mapping เป็นปัญหาที่ยากและเป็นพื้นที่การวิจัยที่แข็งขัน ไม่มีวิธีที่รับประกันความสำเร็จ แต่มีแนวทางที่แนะนำและตัวอย่างของปัญหาที่เรารู้วิธี map แล้ว

แนวทางแรกคือให้คอมพิวเตอร์คลาสสิกทำงานใด ๆ ที่พวกมันเก่งกว่า งานที่ง่ายสำหรับคอ�มพิวเตอร์คลาสสิกน่าจะไม่ได้ประโยชน์จากคอมพิวเตอร์ควอนตัม คอมพิวเตอร์ควอนตัมสำหรับปัญหาที่ยากในเชิง classical แน่นอนว่าหากนี่เป็นครั้งแรกที่คุณใช้ Qiskit หรือคอมพิวเตอร์ควอนตัม อย่ากังวลเกี่ยวกับการหาปัญหาที่ซับซ้อนในการคำนวณ แบ่งมันเป็นปัญหาขนาดเล็กที่คุณสามารถเรียนรู้ได้ก่อนที่จะไปตรงสู่โครงการ utility-scale

ต่อไป แปลผลลัพธ์สำหรับปัญหาของคุณที่คุณต้องการวัดหรือเข้าใจเป็นค่าความคาดหวังหรือ cost function Cost function คือฟังก์ชันเฉพาะปัญหาที่กำหนดเป้าหมายของปัญหาเป็นสิ่งที่จะลดหรือสูงสุด สามารถใช้เพื่อดูว่า trial state หรือโซลูชันทำงานได้ดีเพียงใดเทียบกับเป้าหมายนั้น แนวคิดนี้สามารถนำไปใช้กับการประยุกต์ใช้ต่าง ๆ ในเคมี machine learning การเงิน การปรับให้เหมาะสม และอื่น ๆ ไม่จำเป็นว่าคุณกำลังเข้าถึงปัญหาจากสาขาวิชาใด

ยังต้องจำไว้ว่าฮาร์ดแวร์�ที่คุณจะใช้มี topology เฉพาะดังที่เราพูดถึงในส่วนฮาร์ดแวร์ Qubit บางตัวเชื่อมต่อกัน และบางตัวไม่ คุณจะต้อง map ปัญหาของคุณสู่ circuit ที่เคารพ topology heavy-hex ของโปรเซสเซอร์ IBM quantum

สำหรับตอนนี้ สิ่งสำคัญที่สุดที่ต้องจำคือขั้นตอนนี้ต้องการการฝึกฝน คุณต้องมีความเข้าใจที่ดีไม่เพียงแต่ปัญหาของคุณ แต่ยังความสามารถของฮาร์ดแวร์ด้วย และเราจะผ่านตัวอย่างและ use case เฉพาะในบทเรียนอนาคตเพื่อดูวิธีสมดุลข้อพิจารณาทั้งหมดเหล่านี้

Optimize

ต่อไป เราจะต้องเลือกโปรเซสเซอร์ควอนตัมที่มี Qubit เพียงพอที่มีคุณภาพเพียงพอที่เราสามารถรัน quantum circuit ของเราได้ ตัดสินใจเหล่านี้โดยยึดตาม metrics สามอย่างที่เราพูดถึงในส่วนฮาร์ดแวร์: qubit count, EPLG, และ CLOPS

จากนั้นเราปรับให้เหมาะสม circuit ของเราสำหรับฮ�าร์ดแวร์ที่เลือก ก่อนอื่น เราต้อง layout และ route circuit ของเราอย่างมีประสิทธิภาพ Layout หมายถึงการ map virtual Qubit ใน circuit สู่ physical Qubit บนโปรเซสเซอร์ Routing หมายถึงการปรับ circuit เพื่อให้การเชื่อมต่อระหว่าง virtual Qubit ใน circuit ตรงกับการเชื่อมต่อของ physical Qubit บนโปรเซสเซอร์ มีสองสิ่งที่ต้องจำในระหว่างขั้นตอน layout และ routing

-

ไม่ใช่ Qubit ทั้งหมดที่เชื่อมต่อกัน บางตัวอยู่ห่างไกลมากบนชิป และเราต้องลดหรือขจัดการมีปฏิกิริยาระยะยาวทุกที่ที่เป็นไปได้ คุณสามารถใช้ชุดของ SWAP Gate ระหว่าง Qubit ที่อยู่ติดกันเพื่อย้ายข้อมูล Qubit ไปรอบ ๆ แต่ SWAP Gate มีค่าใช้จ่ายสูงและเกิดข้อผิดพลาดได้ง่าย ดังนั้นอาจมีวิธีที่ดีกว่า พยายามหลีกเลี่ยง SWAP Gate ที่มีค่าใช้จ่ายสูงมากเกินไป

-

Layout และ routing เป็นกระบวนการ iterative คุณสามารถทำด้วยมือ แต่ยังมีเครื่องมือ Qiskit ที่เรียกว่า

mapomaticซึ่งสามารถให้คำแนะนำสำหรับ physical qubit layout ตาม approximate error rate Transpiler (ที่เราจะพูดถึงในไม่ช้า) ยังสามารถให้คำแนะนำที่มีข้อมูลได้

ต่อไป เราสามารถประกอบลำดับของ single-qubit Gate ที่ทำงานบน Qubit เดียวกันเป็น single Gate และบางครั้งก็กำจัด Gate ที่ไม่จำเป็นหรือชุดของ Gate ออกได้ ตัวอย่างเช่น ชุดของ Gate บางอย่างสามารถลดเป็นชุดที่เรียบง่ายกว่า และจริง ๆ แล้ว บางครั้งชุดของ Gate อาจเท่ากับ identity operation ดังนั้นเราสามารถขจัดพวกมันออกได้ คุณสามารถทำสิ่งนี้โดยอัตโนมัติโดยใช้ Qiskit Transpiler แต่คุณยังสามารถทำด้วยตนเองทีละ Gate หากต้องการควบคุมมากขึ้น

เมื่อเราปรับปรุง circuit layout, routing และ gate count แล้ว ไม่ว่าจะด้วยมือหรือโดยใช้ Transpiler เราปกติต้องการแสดงภาพ circuit ของเราเพื่อให้แน่ใจว่า timing ของ Gate ทั้งหมดสมเหตุสมผล มี argument ที่คุณสามารถตั้งค่าใน Transpiler เพื่อแสดงภาพ timeline ของ circuit ของคุณ และตรวจสอบให้แน่ใจว่าทุกอย่างเรียงตามที่คุณคาดหวัง

Qiskit Transpiler

ดังที่กล่าวไว้ก่อนหน้า Qiskit Transpiler สามารถใช้ช่วยในขั้นตอนแรกของ patterns workflow ตอนนี้มาเจาะลึกความสามารถของมันในรายละเอียดมากขึ้น มันสามารถเขียน input circuit ที่กำหนดใหม่เพื่อให้ตรงกับ topology ของอุปกรณ์ควอนตัมเฉพาะและปรับ circuit ให้เหมาะสมสำหรับการรันและความทนทานต่อสัญญาณรบกวน มันยังเขียน circuit ที่กำหนดใหม่เป็น basis Gate ของโปรเซสเซอร์ควอนตัมเฉพาะที่คุณเลือก

Qiskit มี transpilation pipeline ในตัวสี่อย่างที่สอดคล้องกับ optimization level ต่างกัน และเว้นแต่คุณคุ้นเคยกับการปรับให้เหมาะสม quantum circuit อยู่แล้ว เราแนะนำให้ใช้หนึ่งในนั้น โดยค่าเริ่มต้น กระบวนการ transpilation รวมหกขั้นตอนเหล่านี้:

-

Initialization ขั้นตอนนี้รัน pass เริ่มต้นที่จำเป็นก่อนที่เราจะเริ่ม embed circuit บน backend ซึ่งปกติเกี่ยวข้องกับการ unroll custom instruction และแปลง circuit เป็นเพียง single- และ two-qubit Gate

-

Layout ขั้นตอนนี้ map virtual Qubit ใน circuit สู่ physical Qubit บน backend ดู Layout Stage สำหรับรายละเอียดเพิ่มเติม

-

Routing ขั้นตอนนี้รันหลังจาก layout ถูก apply และ inject Gate (เช่น swap gate) เข้าใน circuit เดิมเพื่อให้เข้ากันได้กับการเชื่อมต่อของ backend ดู Routing Stage สำหรับรายละเอียดเพิ่มเติม

-

Translation ขั้นตอนนี้แปล Gate ใน circuit สู่ basis set ของ target backend ดู Translation Stage สำหรับรายละเอียดเพิ่มเติม

-

Optimization ขั้นตอนนี้รัน main optimization loop ซ้ำ ๆ จนกว่าจะถึงเงื่อนไข (เช่นการบรรลุ target depth บางอย่าง) เรามี optimization level สี่อย่างที่แตกต่างกันให้เลือก ที่อธิบายด้านล่าง

-

Scheduling ขั้นตอนนี้สำหรับ hardware-aware scheduling pass ในระดับสูง การ scheduling สามารถคิดได้ว่าเป็นการแทรก delay เข้าใน circuit เพื่อบัญชี idle time บน Qubit ระหว่างการรัน instruction

มี optimization level สี่อย่างตั้งแต่ 0 ถึง 3 โดยที่ optimization level สูงกว่าใช้เวลาและความพยายามในการคำนวณมากกว่าแต่อาจให้ circuit ที่ดีกว่า Optimization level 0 มีไว้สำหรับการทดลอง characterization ของอุปกรณ์ และด้วยเหตุนี้ จึง map เพียง input circuit สู่ข้อจำกัดของ target backend โดยไม่ทำการปรับให้เหมาะสมใด ๆ Optimization level 3 ใช้ความพยายามมากที่สุดในการปรับให้เหมาะสม circuit อย่างไรก็ตาม เนื่องจากเทคนิคการปรับให้เหมาะสมหลายอย่างใน Transpiler อิงตาม heuristic การใช้ความพยายามในการคำนวณมากขึ้นไม่ได้ผลให้คุณภาพของ circuit ที่ output ดีขึ้นเสมอไป หากสนใจเพิ่มเติม ดูเอกสาร transpiler ใน Qiskit

การระงับข้อผิดพลาด

ขั้นตอนแรกในการลดข้อผิดพลาดใน circuit คือการปรับ layout, routing ให้เหมาะสมและลดจำนวน Gate ซึ่งเราได้ทำแล้ว ไม่ว่าจะใช้ Transpiler หรือทำเอง ตอนนี้มาพูดถึงวิธีการที่ซับซ้อนกว่าของการระงับข้อผิดพลาด

การระงับข้อผิดพลาดหมายถึงกลุ่มของเทคนิคที่แปลง circuit ระหว่างการ compile เพื่อลดข้อผิดพลาด มันแตกต่างจากการลดข้อผิดพลาด ซึ่งเราจะพูดถึงในภายหลังในส่วน "Execute" ด้านล่าง รูปแบบที่พบบ่อยที่สุดสองอย่างของการระงับข้อผิดพลาดที่เราใช้คือ dynamical decoupling และ Pauli twirling:

- Dynamical decoupling ถูกใช้เพื่อยกเลิกสัญญาณรบกวนสิ่งแวดล้อมบางส่วนที่เกิดขึ้นเมื่อ Qubit นั่งอยู่เฉย ๆ โดยการใช้ชุดของ Gate ในเวลาเฉพาะ คุณสามารถทำให้สัญญาณรบกวนที่สะสมในส่วนหนึ่งของช่วงเวลาที่ไม่ใช้งานยกเลิกสัญญาณรบกวนในส่วนอื่น ๆ ประมาณ

- Pauli twirling เป็นวิธีการแทรก Gate สุ่มไม่ใช่เพื่อยกเลิกสัญญาณรบกวน ดังเช่นใน dynamical decoupling แต่เพื่อลดความซับซ้อนของสัญญาณรบกวน โดยการแทรก Gate สุ่ม มันป้องกันผลกระทบของข้อผิดพลาดต่าง ๆ จากการสะสมเร็ว และทำให้สัญญาณรบกวนง่ายต่อการ characterize มากขึ้น เนื่องจากตอนนี้มีลักษณะ stochastic วิธีนี้ยังเป็นพื้นฐานของเทคนิคการลดข้อผิดพลาดที่มีพลังซึ่งเราจะพูดถึงด้านล่าง

Execute

ตอนนี้เราพร้อมที่จะรัน quantum program แล้ว Qiskit Runtime primitives ให้ interface กับฮาร์ดแวร์ IBM Quantum และยัง abstract การระงับและลดข้อผิดพลาดออกจากผู้ใช้ มี primitive ให้เลือกสองตัว: Sampler และ Estimator

Qiskit Runtime's Sampler รัน circuit หลาย ๆ ครั้งบนอุปกรณ์ควอนตัม ทำการวัดในแต่ละรัน และสร้างการกระจายความน่าจะเป็นใหม่จาก bit string ที่ได้ ยิ่ง run (หรือ shot) มาก ผลลั�พธ์จะยิ่งแม่นยำ แต่ต้องใช้เวลาและทรัพยากรควอนตัมมากขึ้น โดยเฉพาะอย่างยิ่ง มันคำนวณความน่าจะเป็นของการได้รับ standard basis state ที่เป็นไปได้แต่ละอย่างโดยการวัดสถานะที่เตรียมโดย circuit

Qiskit Runtime's Estimator ใช้กระบวนการ algebraic ที่ซับซ้อนเพื่อประมาณค่าความคาดหวังบนอุปกรณ์ควอนตัมจริงโดยการแบ่ง observable เป็นชุดของ observable อื่น ๆ ที่มี eigenbasis ที่รู้จัก

ขั้นตอน Execute ยังเป็นเวลาที่เราสามารถเลือกกลยุทธ์ การลดข้อผิดพลาด การลดข้อผิดพลาด หมายถึงเทคนิคที่ช่วยให้ผู้ใช้ลดข้อผิดพลาดของ circuit โดยการสร้างแบบจำลองสัญญาณรบกวนของอุปกรณ์ที่มีอยู่ในเวลาของการรัน ปกติสิ่งนี้ส่งผลให้เกิดค่าใช้จ่าย quantum pre-processing ที่เกี่ยวข้องกับการฝึก model และค่าใช้จ่าย classical post-processing เพื่อลดข้อผิดพลาดในผลลัพธ์ raw โดยใช้ model ที่สร้าง แลกกับค่าใช้จ่ายนี้ เราสามารถได้ผลลัพธ์ที่แม่นยำกว่ามาก

มีเทคนิคหลายอย่างที่เราสามารถใช้สำหรับการลดข้อผิดพลาด เราจะพูดถึงสามอย่าง ในลำดับที่เพิ่มขึ้นของความทนทานต่อข้อผิดพลาด แต่ยังในลำดับที่เพิ่มขึ้นของค่าใช้จ่ายในการคำนวณ อย่างไรก็ตาม โปรดทราบว่านี่เป็นพื้นที่การวิจัยที่แข็งขัน ดังนั้นเราน่าจะยังคงคิดค้นสิ่งใหม่และปรับปรุงสิ่งเก่าต่อไป

ที่ resilience level 0 Transpiler ไม่ทำอะไรกับ circuit ของคุณ

ที่ level 1 มันนำวิธีการที่เรียกว่า Twirled Readout Error eXtinction (T-REX) มาใช้ T-REX ใช้ Pauli twirling ดังที่พูดถึงในส่วนการระงับข้อผิดพลาด ดังที่กล่าวไว้ การแทรก Gate สุ่มเข้าใน circuit สามารถทำให้แม้แต่สัญญาณรบกวนที่ซับซ้อนและยากในการสร้างแบบจำลองดู stochastic และง่ายต่อการบัญชีหรือลบออกใน post-processing

ที่ resilience level 2 Zero Noise Extrapolation (ZNE) ถูกเพิ่ม นี่เป็นเทคนิคที่ได้รับความนิยมที่เราประสบความสำเร็จล่าสุ�ดมาก แนวคิดเบื้องหลัง ZNE อาจน่าประหลาดใจเล็กน้อย เราเพิ่มสัญญาณรบกวนบนสิ่งที่มีอยู่แล้ว! แต่สิ่งนี้ช่วยให้เราสามารถ extrapolate ในทิศทางกลับ เพื่อทำนายว่าผลลัพธ์จะเป็นอย่างไรหากมีสัญญาณรบกวนน้อยลงเรื่อย ๆ

การเพิ่มสัญญาณรบกวนสามารถทำได้หลายวิธี ตัวอย่างเช่น เราสามารถยืด Gate ให้ยาวขึ้นและด้วยเหตุนี้จึงเกิดข้อผิดพลาดได้ง่ายขึ้น หรือรัน Gate เพิ่มเติมที่ในที่สุดส่งผลให้เป็น identity operation ดังนั้น circuit จึงไม่เปลี่ยนแปลงในเชิงฟังก์ชัน แต่เราตั้งใจสุ่มสัญญาณรบกวนมากขึ้น อย่างไรก็ตาม คุณต้องทำสิ่งนี้สำหรับ circuit ทุกตัวและทุกค่าความคาดหวังที่คุณต้องการติดตาม ดังนั้นคุณสามารถเห็นว่ามันอาจมีค่าใช้จ่ายสูงในการคำนวณ

ZNE ชนิดเฉพาะหนึ่งเรียกว่า Probabilistic Error Amplification (PEA) เมื่อเราเรียนรู้ noise model สำหรับ Gate แล้ว PEA ทำงานโดยการสุ่มข้อผิดพลาดจาก noise model นั้นและ inject พวกมันเข้าไปใน circuit โดยตั้งใจ ยังไม่มีใน Qiskit แต่จะมีในปลายปีนี้

รูปแบบสุดท้ายของการลดข้อผิดพลาดที่เราจะพูดถึงคือ Probabilistic Error Cancellation (PEC) แทนที่จะอยู่ที่ resilience level 3 PEC เป็นความสามารถพิเศษที่คุณต้องเปิดด้วยตนเองใน Qiskit เพราะทรัพยากรการคำนวณที่ต้องการไม่ปรับขนาดได้ดีเมื่อเปรียบเทียบกับเทคนิคการลดข้อผิดพลาดอื่น ๆ คุณเริ่มต้นด้วยการเรียนรู้เกี่ยวกับสัญญาณรบกวนที่ส่งผลต่อ circuit ของคุณ รัน noise-learning หรือ noise-characterization circuit สำหรับแต่ละ layer ของ two-qubit Gate ที่ไม่ซ้ำกันใน circuit ของคุณ ผลลัพธ์เหล่านี้ช่วยให้คุณอธิบายสัญญาณรบกวนในแง่ของ Pauli operator เมื่อคุณรู้ noise term เหล่านี้ คุณสามารถปรับ circuit ของคุณเพื่อให้มี Pauli Gate ตรงข้ามในตัวเพื่อยกเลิก noise channel เหล่านี้ในทางใดทางหนึ่ง กระบวนการนี้คล้ายกับวิธีที่หูฟังตัดเสียงรบกวนทำงาน อย่างไรก็ตาม วิธีนี้ของการยกเลิกสัญญาณรบกวนมีค่าใช้จ่ายสูงมาก โดยเวลาในการรันเติบโตอย่างรวดเร็วและแบบเลขชี้กำลังในจำนวน Gate ดังนั้นอาจไม่ใช่ตัวเลือกที่ดีที่สุดสำหรับ circuit ขนาดใหญ่มาก

Post-process

ขั้นตอน post-process คือที่ที่เราแสดงภาพและวิเคราะห์ output ของ quantum circuit ของเรา มีเครื่องมือ Qiskit หลายอย่างให้คุณทำสิ่งนี้ เช่น visualization และ quantum-info module เราจะไม่ครอบคลุมสิ่งเหล่านี้ที่นี่ แต่เราจะเห็น module เหล่านี้ในการทำงานเมื่อเราเจาะลึกตัวอย่างการประยุกต์ใช้ในบทเรียนอนาคต

บทสรุป

หวังว่าบทเรียนนี้จะให้ tour แบบรวดเร็วของข้อพิจารณาหลักและขั้นตอนการทำงานที่เราใช้เมื่อต้องการรันการประมวลผลควอนตัมระดับ utility scale มันเต็มไปด้วยข้อมูล และหลาย ๆ อย่างจะไม่ซึมซับจนกว่าเราจะเห็นตัวอย่างจริงที่แนวคิดทางทฤษฎีเหล่านี้ถูกนำไปใช้จริง ดังนั้น นั่นคือสิ่งที��่ส่วนที่เหลือของคอร์สจะเป็น ท้ายที่สุด คอร์สนี้ไม่ได้เรียกว่า Quantum Computing in Practice โดยไม่มีเหตุผล!

ครั้งหน้า เราจะดูตัวอย่างเฉพาะว่าจะใช้ Qiskit patterns workflow เพื่อออกแบบและรัน quantum circuit ที่แก้ปัญหาคลาสสิกจากทฤษฎีกราฟที่เรียกว่า MaxCut ได้อย่างไร